PCI-SIG Wraps Up Development of PCIe 7.0 with Record-Breaking Data Speeds

PCI-SIG has reached a critical milestone in developing the next generation of the PCI Express interface by presenting the final draft of the PCIe 7.0 specification (version 0.9). The document is now headed for patent review, with an official release scheduled for 2025, paving the way for future technologies in the coming years.

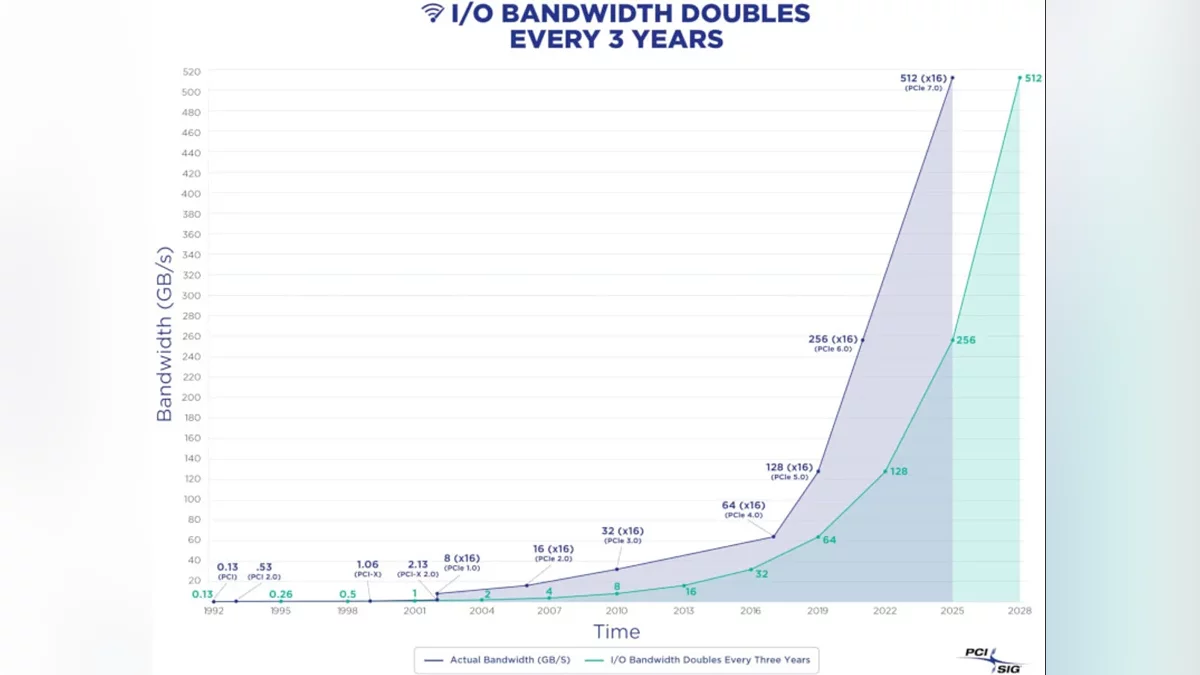

PCIe 7.0 is poised to be a breakthrough, quadrupling the bandwidth compared to PCIe 5.0, which is currently used in most PCs. Thanks to speeds of up to 128 gigatransfers per second (GT/s), the x16 configuration will deliver bidirectional data rates of 512 GB/s. This capability could, for instance, enable the development of SSDs with record-breaking read speeds of up to 50 GB/s—far surpassing today’s devices.

At the heart of the new standard is four-level PAM4 modulation, which optimizes data transmission efficiency even under extreme loads. PCI-SIG engineers have also focused on reducing power consumption, minimizing latency, and extending signal coverage. Additionally, backward compatibility with previous versions ensures a smooth transition for both manufacturers and users.

The new interface is designed for sectors where speed and reliability are critical:

- Artificial Intelligence and Machine Learning – Accelerating data processing for neural networks;

- Cloud Computing and Data Centers – Supporting 800G Ethernet networks and hybrid infrastructures;

- Aerospace – Handling massive real-time data streams;

- Gaming and Graphics – Delivering unprecedented bandwidth for video cards.

It is predicted that the first PCIe 7.0 devices will hit the market between 2027 and 2028. Meanwhile, PCI-SIG is already laying the groundwork for PCIe 8.0, where x16 configurations are expected to reach 1 TB/s, ushering in the era of terabyte speeds. PCIe 7.0 not only sets new benchmarks for the industry but also bridges today’s requirements with tomorrow’s innovations.

-

Goodbye, PhysX: NVIDIA Retires Iconic Technology with RTX 50 Launch

-

Switch 2 to Feature Groundbreaking AI Upscaling Tech, Redefining Portable Gaming

-

Comprehensive GPU Study Reveals the Evolution of Technology

-

AMD unveils technology that simplifies PC upgrades

-

NVIDIA Unveils New DLSS 4 Technology and Highlights Its Key Features